对话昕原:新型存储技术推动半导体技术边界

时间: 2024-10-29 18:00:02 | 作者: 贝博官网

详情

近年间,存算一体技术成为半导体产业的最新热点,既在ISSCC、IEDM等顶级学术会议上引发热点讨论,半导体国际巨头如三星、SK海力士、台积电、英特尔、美光、IBM等也纷纷推出最新研究成果。

举个例子,在今年的ISSCC 2022上,台积电一口气发布了6篇存算一体技术的相关论文,覆盖多种新型存储器类别,其投入之巨可见一斑。

仅以国内市场为例,近年间,一大批如知存科技、九天睿芯、亿铸科技、智芯科微电子、千芯科技和苹芯科技等专注于存算一体的新兴创企纷纷斩获融资或披露进展,市场关注度持续攀升。

近年来,无人驾驶、数据处理中心以及AR/VR元宇宙等高密度计算场景的蓬勃发展,带动了以AI芯片为首的一大批新型半导体技术的爆发。

然而,随着AI芯片走向100Tops、1000Tops甚至更高的算力水平,传统冯·诺伊曼架构却成了制约市场应用的最大瓶颈。

在冯·诺伊曼架构之下,芯片的存储区域和计算区域是分离的,计算时,数据需要在两个区域之间来回搬运。 随着神经网络模型层数、规模以及数据处理量的一直增长,“数据搬运”慢慢的变成了高效能计算性能和功耗的瓶颈,业内俗称“存储墙”。据统计,大算力的AI应用中,数据搬运操作消耗90%的时间和功耗,数据搬运的功耗是运算的650倍。

存算一体,顾名思义,就是将计算单元和存储单元合二为一,用存储单元完成计算工作,从而大幅度减少数据搬运的过程。

冯·诺伊曼架构,承载了过去80年间,计算机技术的爆炸式发展,奠定了整个微电子时代的基础。

当前的存算一体技术路径中,既有使用Flash、SRAM等传统存储器的方案,也有使用ReRAM(RRAM)、PCM、MRAM等新型存储器的方案。

不同方案的适用场景不完全一样。举个例子,Flash方案的运算功耗极低,能够适用于超低功耗的极端边缘应用场景,如超低功耗的语音物联网;但其半导体工艺难以兼容先进节点。

相反,SRAM方案读写速度快,兼容先进工艺节点,能满足高性能计算需求,但其存储密度难以提升,在存储密集场景下难免出现数据搬运的老问题,这会损失一部分存算带来的优势提升,另外SRAM的漏电大的特性也会导致SoC芯片的静态待机功耗大幅提高。

低功耗、大算力、可落地,是否有方案能够解决这“鱼与熊掌不可兼得”的困难问题?

ReRAM全称为阻变存储器,或忆阻器,属于新型非易失性存储技术,断电后不会存在数据丢失问题。

典型的ReRAM由两个电极夹一个薄介电层组成,通过改变上下电极的电压,形成不同的电阻值,进而代表不同的存储状态,实现数据的读写。

ReRAM技术利用阻值特性,可以在存储介质上实现乘法操作,且运行功耗很低,是极优的存内计算介质。

作为新型存储器的代表之一,ReRAM具备读取性能高、读取功耗低、密度高和成本低等特点,可以很好的兼顾大算力、低功耗的存算需求。另外非易失的特性也可以大幅度降低芯片的静态待机功耗。

同时ReRAM技术还能够很好地兼容更为先进的CMOS工艺,满足多种工艺节点的SoC芯片的集成需求。

今年上半年,国内勇于探索商业模式的公司昕原半导体宣布,其大陆首条28/22nm ReRAM 12寸中试生产线正式完成装机验收,并在工控领域达成量产商用。

这是中国大陆第一条28/22nm ReRAM 12寸中试生产线,中国大陆第一次在ReRAM赛道与国际同行处于同一个起跑线上,也为存算一体的发展注入了新势能。

昕原半导体新技术研究院负责人周博士告诉36氪,存算一体的设计是“存”与“算”耦合设计,是一个交替提升的过程。这也代表着,存算一体从实验室走到商业应用的过程中,不仅仅需要团队拥有顶级计算设计能力,还需要对存储、对器件本身就具有深度的认知和一直在改进的能力,能够准确的通过器件特性进行一定的优化与性能加深设计。

“比如我们器件的高低阻值、开关比、读写IV曲线都会影响存算电路的设计,这会体现到最终的性能与能耗数据上,我们大家可以根据我们器件的特点做‘定制’设计与优化,这样整体的性能能够获得最大提升;同时我们器件和制程工艺也在不断的迭代优化中,这样产品与器件能做到良性循环” 周博士告诉36氪。

相对而言,单独计算芯片设计大都有迹可循,有一定难度但并不是无法达成的任务;而存储器件的性能迭代以及存算耦合设计能力才真正的考验团队的能力。存储器件和工艺制程的迭代的设计往往要求具有一条芯片产线能力,产线不仅意味着设备同时还要求专业的运营、工艺制程团队、器件设计能力,只有四者合一才能具备器件迭代能力。

因此在传统的存储领域,只有像三星、美光和英特尔这样的大厂具备器件迭代能力。

在新型存储领域,昕原是目前国内唯一具备ReRAM器件和工艺制程高速迭代优化设计能力的团队,不仅有自己的中试生产线,也拥有完整专业的工艺制程开发、器件开发、芯片数模设计、存储设计团队。只有将“存”与“算”结合,才能做出真正具有竞争力的产品。

当前,基于其ReRAM技术,昕原半导体的产品线聚焦在新型存储SoC芯片、AI存算模块/IP、高性能SoC芯片这三大应用方向。

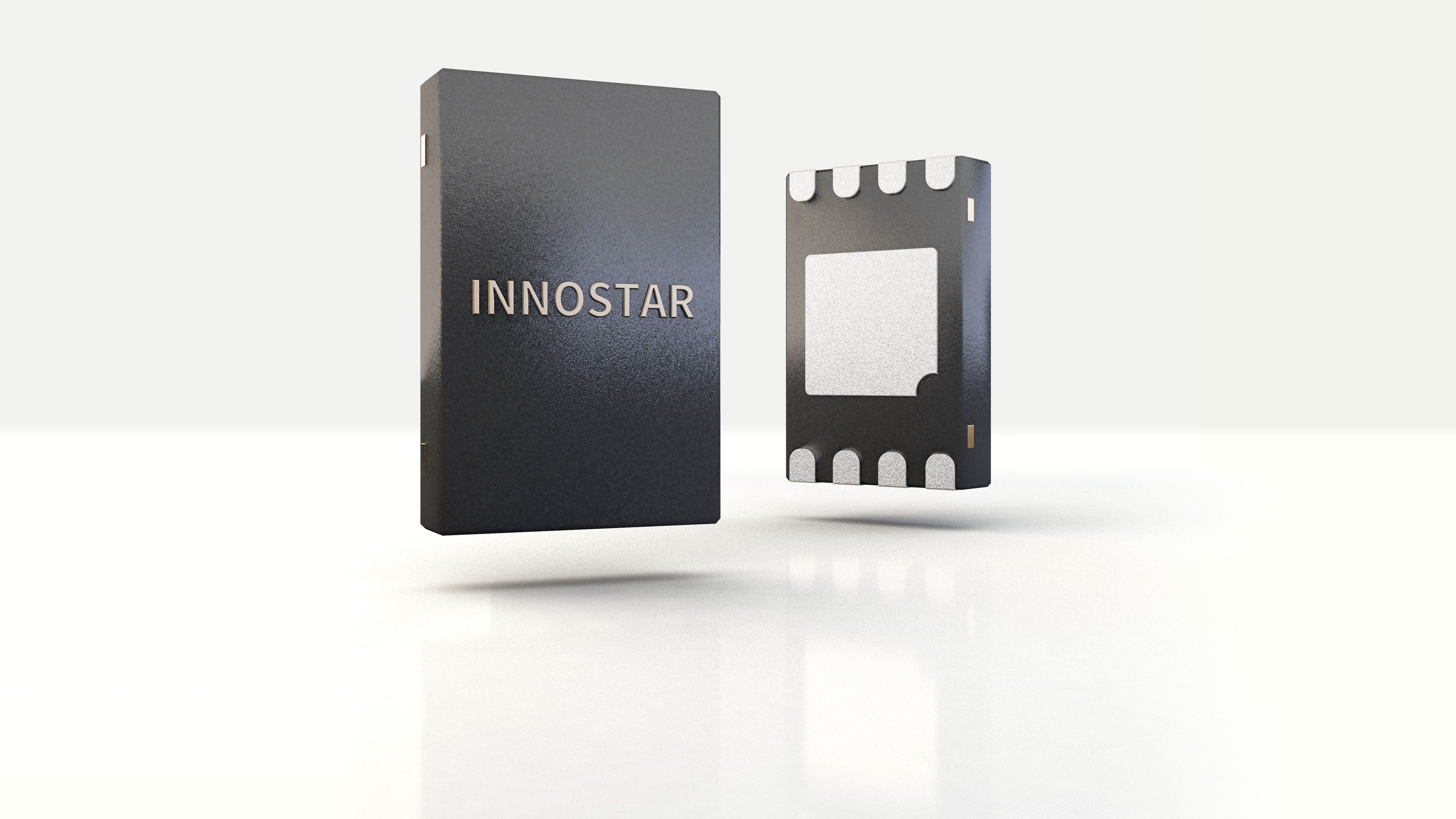

在SoC方向,昕原推出了28nm制程的ReRAM安全存储芯片“昕·山文”系列。该系列芯片目前已在工控领域头部企业禾川科技的产线上量产商用。 基于ReRAM PUF(Physical Unclonable Function-物理不可克隆函数)技术的“昕·山文”具有自生唯一性和物理不可克隆性两大安全特性,为系统提供了更高的抗物理攻击安全性。

在AI存算方向上,以昕原第一代的ReRAM存算加速阵列为核心的存算芯片产品即将流片,采用28nm制程工艺,能效比能做到优于传统AI芯片一个数量级。下一代更高密度的、基于22nm制程工艺的存算加速阵列也在开发中。

存算一体相比传统AI芯片技术仍然比较年轻,新技术的商业落地需要学术界与产业界一起努力。昕原作为国内最早实现ReRAM技术商业化落地的公司,能够给大家提供成熟的ReRAM存储介质、中试生产线的流片能力、不断迭代的器件开发能力、完整的电路设计能力与产业界、学术界的朋友一起建设存算一体的生态圈。

昕原半导体“具有选择和控制晶体管的电阻式随机访问存储器和架构”专利获授权

全国28省105个团队竞逐决赛,2024年中兴捧月“星匠师”巧匠精英挑战赛圆满落幕